# Shadow Red DDR4 UDIMM Memory Module Specifications

| Revision No. | History         | Draft Date | Remark |

|--------------|-----------------|------------|--------|

| 1.0          | Initial Release | May.2022   |        |

# **Ordering Information Table**

| Model           | Туре       | Capacity        | Speed   | Latency     | Voltage |

|-----------------|------------|-----------------|---------|-------------|---------|

| NTSDD4P36DP-16R | DDR4 UDIMM | 16GB (8GB x 2)  | 3600MHz | 18-22-22-42 | 1.35V   |

| NTSDD4P32DP-32R | DDR4 UDIMM | 32GB (16GB x 2) | 3200MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P32DP-16R | DDR4 UDIMM | 16GB (8GB x 2)  | 3200MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P30DP-32R | DDR4 UDIMM | 32GB (16GB x 2) | 3000MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P30DP-16R | DDR4 UDIMM | 16GB (8GB x 2)  | 3000MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P26DP-32R | DDR4 UDIMM | 32GB (16GB x 2) | 2666MHz | 19-19-19-43 | 1.2V    |

| NTSDD4P26DP-16R | DDR4 UDIMM | 16GB (8GB x 2)  | 2666MHz | 19-19-19-43 | 1.2V    |

| NTSDD4P36SP-16R | DDR4 UDIMM | 16GB            | 3600MHz | 18-22-22-42 | 1.35V   |

| NTSDD4P36SP-08R | DDR4 UDIMM | 8GB             | 3600MHz | 18-22-22-42 | 1.35V   |

| NTSDD4P32SP-16R | DDR4 UDIMM | 16GB            | 3200MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P32SP-08R | DDR4 UDIMM | 8GB             | 3200MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P30SP-16R | DDR4 UDIMM | 16GB            | 3000MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P30SP-08R | DDR4 UDIMM | 8GB             | 3000MHz | 16-20-20-40 | 1.35V   |

| NTSDD4P26SP-16R | DDR4 UDIMM | 16GB            | 2666MHz | 19-19-19-43 | 1.2V    |

| NTSDD4P26SP-08R | DDR4 UDIMM | 8GB             | 2666MHz | 19-19-19-43 | 1.2V    |

## Description

Netac Unbuffered DDR4 SDRAM DIMMs (Unbuffered Double Data Rate Synchronous DRAM Dual In-Line Memory Modules) are low power, high-speed operation memory modules that use DDR4 SDRAM devices. Each 288- pin DIMM uses gold contact fingers. The SDRAM Unbuffered DIMM is intended for use as main memory when installed in systems such as PCs.

## Features

- Specially designed aluminum alloy heat Spreader

- On-board I<sup>2</sup> serial presence-detect (SPD) EEPROM

- Fixed burst chop (BC) of 4 and burst length (BL) of 8 via the mode register set (MRS)

- Databus write cyclic redundancy check (CRC)

- Temperature controlled refresh (TCR)

- Command/Address (CA) parity

- Per DRAM Addressability is supported

- 8 bit pre-fetch

- Fly-by topology

- Command/Address latency (CAL)

- Terminated control command and address bus

- PCB: Height 1.23" (31.25mm)

- Gold edge contacts

- RoHS Compliant and Halogen-Free

# **Pin Assignments**

| Pin | Front Side        | Pin | Back Side | Pin | Front Side        | Pin | Back Side |

|-----|-------------------|-----|-----------|-----|-------------------|-----|-----------|

| 1   | NC                | 145 | NC        | 74  | CK0_t             | 218 | CK1_t     |

| 2   | VSS               | 146 | VREFCA    | 75  | CK0_c             | 219 | CK1_c     |

| 3   | DQ4               | 147 | VSS       | 76  | VDD               | 220 | VDD       |

| 4   | VSS               | 148 | DQ5       | 77  | VTT               | 221 | VTT       |

| 5   | DQ0               | 149 | VSS       |     | KEV               |     |           |

| 6   | VSS               | 150 | DQ1       |     | KEY               |     |           |

| 7   | DM0_n, DBI0_n, NC | 151 | VSS       | 78  | EVENT_n           | 222 | PARITY    |

| 8   | NC                | 152 | DQS0_c    | 79  | A0                | 223 | VDD       |

| 9   | VSS               | 153 | DQS0_t    | 80  | VDD               | 224 | BA1       |

| 10  | DQ6               | 154 | VSS       | 81  | BA0               | 225 | A10/AP    |

| 11  | VSS               | 155 | DQ7       | 82  | RAS_n/A16         | 226 | VDD       |

| 12  | DQ2               | 156 | VSS       | 83  | VDD               | 227 | RFU       |

| 13  | VSS               | 157 | DQ3       | 84  | CS0_n             | 228 | WE_n/A14  |

| 14  | DQ12              | 158 | VSS       | 85  | VDD               | 229 | VDD       |

| 15  | VSS               | 159 | DQ13      | 86  | CAS_n/A15         | 230 | NC        |

| 16  | DQ8               | 160 | VSS       | 87  | ODT0              | 231 | VDD       |

| 17  | VSS               | 161 | DQ9       | 88  | VDD               | 232 | A13       |

| 18  | DM1_n, DBI1_n, NC | 162 | VSS       | 89  | CS1_n             | 233 | VDD       |

| 19  | NC                | 163 | DQS1_c    | 90  | VDD               | 234 | NC        |

| 20  | VSS               | 164 | DQS1_t    | 91  | ODT1              | 235 | NC        |

| 21  | DQ14              | 165 | VSS       | 92  | VDD               | 236 | VDD       |

| 22  | VSS               | 166 | DQ15      | 93  | NC                | 237 | NC        |

| 23  | DQ10              | 167 | VSS       | 94  | VSS               | 238 | SA2       |

| 24  | VSS               | 168 | DQ11      | 95  | DQ36              | 239 | VSS       |

| 25  | DQ20              | 169 | VSS       | 96  | VSS               | 240 | DQ37      |

| 26  | VSS               | 170 | DQ21      | 97  | DQ32              | 241 | VSS       |

| 27  | DQ16              | 171 | VSS       | 98  | VSS               | 242 | DQ33      |

| 28  | VSS               | 172 | DQ17      | 99  | DM4_n, DBI4_n, NC | 243 | VSS       |

| 29  | DM2_n, DBI2_n, NC | 173 | VSS       | 100 | NC                | 244 | DQS4_c    |

| 30  | NC                | 174 | DQS2_c    | 101 | VSS               | 245 | DQS4_t    |

| 31  | VSS               | 175 | DQS2_t    | 102 | DQ38              | 246 | VSS       |

| 32  | DQ22              | 176 | VSS       | 103 | VSS               | 247 | DQ39      |

| 33  | VSS               | 177 | DQ23      | 104 | DQ34              | 248 | VSS       |

| 34  | DQ18              | 178 | VSS       | 105 | VSS               | 249 | DQ35      |

| 35  | VSS               | 179 | DQ19      | 106 | DQ44              | 250 | VSS       |

| 36  | DQ28              | 180 | VSS       | 107 | VSS               | 251 | DQ45      |

# Netac

### Shadow Red DDR4 288-Pin UDIMM

| Shadow Red DDR4 288-Pill ODIMIN |                   |     |         |     |                   |     |        |

|---------------------------------|-------------------|-----|---------|-----|-------------------|-----|--------|

| 37                              | VSS               | 181 | DQ29    | 108 | DQ40              | 252 | VSS    |

| 38                              | DQ24              | 182 | VSS     | 109 | VSS               | 253 | DQ41   |

| 39                              | VSS               | 183 | DQ25    | 110 | DM5_n, DBI5_n, NC | 254 | VSS    |

| 40                              | DM3_n, DBI3_n, NC | 184 | VSS     | 111 | NC                | 255 | DQS5_C |

| 41                              | NC                | 185 | DQS3_c  | 112 | VSS               | 256 | DQS5_t |

| 42                              | VSS               | 186 | DQS3_t  | 113 | DQ46              | 257 | VSS    |

| 43                              | DQ30              | 187 | VSS     | 114 | VSS               | 258 | DQ47   |

| 44                              | VSS               | 188 | DQ31    | 115 | DQ42              | 259 | VSS    |

| 45                              | DQ26              | 189 | VSS     | 116 | VSS               | 260 | DQ43   |

| 46                              | VSS               | 190 | DQ27    | 117 | DQ52              | 261 | VSS    |

| 47                              | CB4, NC           | 191 | VSS     | 118 | VSS               | 262 | DQ53   |

| 48                              | VSS               | 192 | CB5, NC | 119 | DQ48              | 263 | VSS    |

| 49                              | CB0, NC           | 193 | VSS     | 120 | VSS               | 264 | DQ49   |

| 50                              | VSS               | 194 | CB1, NC | 121 | DM6_n, DBI6_n, NC | 265 | VSS    |

| 51                              | DM8_n, DBI8_n, NC | 195 | VSS     | 122 | NC                | 266 | DQS6_c |

| 52                              | NC                | 196 | DQS8_c  | 123 | VSS               | 267 | DQS6_t |

| 53                              | VSS               | 197 | DQS8_t  | 124 | DQ54              | 268 | VSS    |

| 54                              | CB6, NC           | 198 | VSS     | 125 | VSS               | 269 | DQ55   |

| 55                              | VSS               | 199 | CB7, NC | 126 | DQ50              | 270 | VSS    |

| 56                              | CB2, NC           | 200 | VSS     | 127 | VSS               | 271 | DQ51   |

| 57                              | VSS               | 201 | CB3, NC | 128 | DQ60              | 272 | VSS    |

| 58                              | RESET_n           | 202 | VSS     | 129 | VSS               | 273 | DQ61   |

| 59                              | VDD               | 203 | CKE1    | 130 | DQ56              | 274 | VSS    |

| 60                              | CKE0              | 204 | VDD     | 131 | VSS               | 275 | DQ57   |

| 61                              | VDD               | 205 | RFU     | 132 | DM7_n, DBI7_n, NC | 276 | VSS    |

| 62                              | ACT_n             | 206 | VDD     | 133 | NC                | 277 | DQS7_c |

| 63                              | BG0               | 207 | BG1     | 134 | VSS               | 278 | DQS7_t |

| 64                              | VDD               | 208 | ALERT_n | 135 | DQ62              | 279 | VSS    |

| 65                              | A12/BC_n          | 209 | VDD     | 136 | VSS               | 280 | DQ63   |

| 66                              | A9                | 210 | A11     | 137 | DQ58              | 281 | VSS    |

| 67                              | VDD               | 211 | A7      | 138 | VSS               | 282 | DQ59   |

| 68                              | A8                | 213 | VDD     | 139 | SA0               | 283 | VSS    |

| 69                              | A6                | 214 | A5      | 140 | SA1               | 284 | VDDSPD |

| 70                              | VDD               | 215 | A4      | 141 | SCL               | 285 | SDA    |

| 71                              | A3                | 215 | VDD     | 142 | VPP               | 286 | VPP    |

| 72                              | A1                | 216 | A2      | 143 | VPP               | 287 | VPP    |

| 73                              | VDD               | 217 | VDD     | 144 | RFU               | 288 | VPP    |

|                                 |                   |     |         |     |                   |     |        |

**Note:** The pin assignment table above is a comprehensive list of all possible pin assignments for DDR4 UDIMM modules. See Functional Block Diagram for pins specific to this module.

# **Pin Descriptions**

| Pin Name                           | Description                                                                                  | Pin Name   | Description                                              |

|------------------------------------|----------------------------------------------------------------------------------------------|------------|----------------------------------------------------------|

| A0-A17 <sup>1</sup>                | SDRAM address bus                                                                            | SCL        | I2C serial bus clock for SPD-TSE                         |

| BA0, BA1                           | SDRAM bank select                                                                            | SDA        | I2C serial bus line for SPD-TSE                          |

| BG0, BG1                           | SDRAM bank group select                                                                      | SA0-SA2    | I2C slave address select for SPD-TSE                     |

| RAS_n <sup>2</sup>                 | SDRAM row address strobe                                                                     | PARITY     | SDRAM parity input                                       |

| CAS_n <sup>3</sup>                 | SDRAM column address strobe                                                                  | VDD        | SDRAM I/OO and core power supply                         |

| WE_n <sup>4</sup>                  | SDRAM write enable                                                                           | C0, C1, C2 | Chip ID lines                                            |

| CS0_n, CS1_n,                      | DIMM Rank Select Lines                                                                       | 12V        | Optional power Supply on socket but<br>not used on UDIMM |

| CKE0, CEK1                         | SDRAM clock enable lines input                                                               | VREFCA     | SDRAM command/address reference<br>supply                |

| ODT0, ODT1                         | SDRAM on-die termination control<br>lines input                                              | VSS        | Power supply return (ground)                             |

| ACT_n                              | SDRAM activate                                                                               | VDDSPD     | Serial SPD-TSE positive power supply                     |

| DQ0-DQ63                           | DIMM memory data bus                                                                         | ALERT_n    | SDRAM ALERT_n output                                     |

| CB0-CB7                            | DIMM ECC check bits                                                                          | VPP        | SDRAM Supply                                             |

| TDQS0_t-TDQS8_t<br>TDQS0_c-TDQS8_c | Dummy loads for mixed populations<br>of x4 based and x8 based RDIMMs.<br>Not used on UDIMMs. |            |                                                          |

| DQS0_t-DQS8_t                      | SDRAM data strobes(positive line of differential pair)                                       |            |                                                          |

| DQS0_c-DQS8_c                      | SDRAM data strobes(negative line of differential pair)                                       | RESET_n    | Set DRAMs to a Known State                               |

| DM0_n-DM8_n,                       | SDRAM data masks/data bus                                                                    | EVENT_n    | SPD signals a thermal event has                          |

| DBI0_n-DBI8_n                      | inersion(x8-based x72 DIMMs)                                                                 |            | occurred                                                 |

| CK0_t, CK1_t                       | SDRAM clock (positive line of<br>differential pair)                                          | VTT        | SDRAM I/O termination supply                             |

| CK0_c, CK1_c                       | SDRAM clock (positive line of<br>differential pair)                                          | RFU        | Reserved for future use                                  |

#### Notes:

- 1. Address A17 is not valid for x8 and x16 based SDRAMs. For UDIMMs, this connection pin is NC.

- 2. RAS\_n is a multiplexed function with A16.

- 3. CAS\_n is a multiplexed function with A15.

- 4. WE\_n is a multiplexed function with A14.

# Input/Output Functional Descriptions

| Symbol                           | Туре   | Function                                                                                                                                                            |

|----------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK0_t, CK0_c,                    | Input  | Clock: CK_t and CK_c are differential clock are sampled on the crossing of the positiveinputs. All address and control input signals edge of CK_t and negative edge |

| CK1_t, CK1_c                     | mput   | of CK_c.                                                                                                                                                            |

|                                  |        | Clock Enable: CKE HIGH activates and CKE LOW deactivates internal clock signals                                                                                     |

|                                  |        | and device input buffers and output drivers. Taking CKE LOW provides Precharge                                                                                      |

|                                  |        | Power Down and Self-Refresh operation (all banks idle), or Active Power-Down (row                                                                                   |

|                                  |        | Active in any bank). CKE is aynchronous for Self-Refresh exit. After VREFCA and                                                                                     |

| CKE0, CKE1                       | Input  | Internal DQ Vref have become stable during the power on and initialization sequence,                                                                                |

|                                  |        | they must be maintained during all operations (including Self-Refresh). CKE must be                                                                                 |

|                                  |        | maintained high throughout read and write accesses. Input buffers, excluding CK_t,                                                                                  |

|                                  |        | CK_c, ODT and CKE, are disabled during power-down. Input buffers, excluding CKE,                                                                                    |

|                                  |        | are disabled during Self-Refresh.                                                                                                                                   |

| CS0_n, CS1_n,                    |        | Chip Select: All commands are masked when CS_n is registered HIGH. CS_n provides                                                                                    |

| CS2_n, CS3_n                     | Input  | for external Rank selection on systems with multiple Ranks. CS_n is considered part                                                                                 |

| 002_11, 000_11                   |        | of the command code. CS2_n and CS_3_n are not used on UDIMMs.                                                                                                       |

|                                  |        | Chip ID: Chip ID is only used for 3DS for 2,4,8 high stack via TSV to select each slice                                                                             |

| C0, C1, C2                       | Input  | of stacked component. Chip ID is considered part of the command code. Not used on                                                                                   |

|                                  |        | UDIMMs.                                                                                                                                                             |

|                                  |        | On-Die Termination: ODT (registered HIGH) enables RTT_NOM termination                                                                                               |

|                                  |        | resistance internal to the DDR4 SDRAM. When enabled, ODT is only applied to each                                                                                    |

|                                  |        | DQ, DQS_t, DQS_c and DM_n/DBI_n/TDQS_t,NU/TDQS_c (When TDQS is enabled                                                                                              |

| ODT0, ODT1                       | Input  | via Mode Register A11=1 in MR1) signal for x8 configurations. For x16 configuration,                                                                                |

|                                  |        | ODT is applied to each DQ, DQSU_t, DQSU_c, DQSL_t, DQSL_c, DMU_n, and                                                                                               |

|                                  |        | DML_n signal. The ODT pin will be ignored if MR1 is programmed to disable                                                                                           |

|                                  |        | RTT_NOM.                                                                                                                                                            |

|                                  |        | Activation Command Input: ACT_n defines the Activation command being entered                                                                                        |

| ACT_n                            | Input  | along with CS_n. The input into RAS_n/A16, CAS_n/A15 and WE_n/A14 will be                                                                                           |

|                                  |        | considered as Row Address A16, A15 and A14.                                                                                                                         |

|                                  |        | Command Inputs: RAS_n/A16, CAS_n/A15 and WE_n/A14 (along with CS_n) define                                                                                          |

| RAS_n/A16,                       |        | the command being entered. Those pins have multi function. For example, for                                                                                         |

| CAS_n/A15,                       | Input  | activation with ACT_n Low, these are Addresses like A16, A15, and A14. But for non-                                                                                 |

| WE_n/A14                         |        | activation command with ACT_n High, these are Command pins for Read, Write, and                                                                                     |

|                                  |        | other commands defined in command truth table.                                                                                                                      |

|                                  |        | Input Data Mask and Data Bus Inversion: DM_n is an input mask signal for write data.                                                                                |

| DM_n/DBI_n/TDQS                  |        | Input data is masked when DM_n is sampled LOW coincident with that input data                                                                                       |

|                                  | Input/ | during a Write access. DM_n is sampled on both edges of DQS. DM is muxed with DBI                                                                                   |

| <sup>ι,</sup><br>(DMU_n/DBIU_n), | Output | function by Mode Register A10, A11, A12 setting in MR5. For x8 device, the function                                                                                 |

| (DML_n/DBIL_n)                   | Julpur | of DM or TDQS is enabled by Mode Register A11 setting in MR1. DBI_n is an                                                                                           |

|                                  |        | input/output identifying whether to store/output the true or inverted data. If DBI_n is                                                                             |

|                                  |        | LOW, the data will be stored/output after inversion inside the DDR4 SDRAM and not                                                                                   |

|                                                    |                  | inverted if DBI_n is HIGH. TDQS is only supported in x8 SDRAM configurations. TDQS is not valid for UDIMMs.                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BG0, BG1                                           | Input            | Bank Group Inputs: BG0 - BG1 define which bank group an Active, Read, Write, or Precharge command is being applied. BG0 also determines which mode register is to be accessed during a MRS cycle. x4/x8 SDRAM configurations have BG0 and BG1. x16 based SDRAMs only have BG0.                                                                                                                                                                                                                               |

| BA0, BA1                                           | Input            | Bank Address Inputs: BA0 - BA1 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                     |

| A0 - A17                                           | Input            | Address Inputs: Provide the row address for ACTIVATE Commands and the column address for Read/Write commands to select one location out of the memory array in the respective bank. A10/AP, A12/BC_n, RAS_n/A16, CAS_n/A15 and WE_n/A14 have additional functions. See other rows. The address inputs also provide the op-code during Mode Register Set commands. A17 is only defined for the x4 SDRAM configuration.                                                                                        |

| A10 / AP                                           | Input            | Auto-precharge: A10 is sampled during Read/Write commands to determine whether<br>Autoprecharge should be performed to the accessed bank after the Read/Write<br>operation. (HIGH: Autoprecharge; LOW: no Autoprecharge). A10 is sampled during a<br>Precharge command to determine whether the Precharge applies to one bank (A10<br>LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is<br>selected by bank addresses.                                                         |

| A12 / BC_n                                         | Input            | Burst Chop: A12/BC_n is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                    |

| RESET_n                                            | CMOS<br>Input    | Active Low Asynchronous Reset: Reset is active when RESET_n is LOW, and inactive when RESET_n is HIGH. RESET_n must be HIGH during normal operation.                                                                                                                                                                                                                                                                                                                                                         |

| DQ                                                 | Input/<br>Output | Data Input/ Output: Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0-DQ3 may indicate the internal Vref level during test via Mode Register Setting MR4 A4=High. Refer to vendor specific data sheets to determine which DQ is used.                                                                                                                                                                                            |

| DQS_t, DQS_c,<br>DQSU_t, DQSU_c,<br>DQSL_t, DQSL_c | Input/<br>Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For the x16, DQSL corresponds to the data on DQL0-DQL7; DQSU corresponds to the data on DQU0-DQU7. The data strobe DQS_t, DQSL_t and DQSU_t are paired with differential signals DQS_c, DQSL_c, and DQSU_c, respectively, to provide differential pair signaling to the system during reads and writes. DDR4 SDRAM supports differential data strobe only and does not support single-ended. |

| TDQS_t, TDQS_c                                     | Output           | Termination Data Strobe: TDQS_t/TDQS_c are not valid for UDIMMs.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PARITY                                             | Input            | Command and Address Parity Input : DDR4 Supports Even Parity check in DRAMs with MR setting. Once it's enabled via Register in MR5, then DRAM calculates Parity with ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14, BG0-BG1, BA0-BA1, A16-A0. Input parity should be maintained at the rising edge of the clock and at the same time with command & address with CS_n LOW.                                                                                                                                           |

## **Absolute Maximum Ratings**

#### **Absolute Maximum DC Ratings**

| Symbol    | Parameter                                        | Rating      | Units | NOTE  |

|-----------|--------------------------------------------------|-------------|-------|-------|

| VDD       | Voltage on VDD pin relative to Vss               | -0.3 ~ 1.5  | V     | 1,3   |

| VDDQ      | Voltage on VDDQ pin relative to Vss              | -0.3 ~ 1.5  | V     | 1,3   |

| VPP       | Voltage on VPP pin relative to Vss               | -0.3 ~ 3.0  | V     | 4     |

| VIN, VOUT | Voltage on any pin except VREFCA relative to Vss | -0.3 ~ 1.5  | V     | 1,3,5 |

| TSTG      | Storage Temperature                              | -55 to +100 | °C    | 1,2   |

#### Note:

- Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 3. VDD and VDDQ must be within 300mV of each other at all times; and VREFCA must be not greater than 0.6 x VDDQ, When VDD and VDDQ are less than 500mV; VREFCA may be equal to or less than 300mV.

- 4. VPP must be equal or greater than VDD/VDDQ at all times.

- 5. Overshoot area above 1.5V is specified in DDR4 Device Operation.

#### DRAM Component Operating Temperature Range

| Symbol | Parameter                          | Rating   | Units | Notes |

|--------|------------------------------------|----------|-------|-------|

| TOPER  | Normal Operating Temperature Range | 0 to 85  | °C    | 1,2   |

| IOPER  | Extended Temperature Range         | 85 to 95 | °C    | 1,3   |

#### Notes:

1. Operating Temperature TOPER is the case surface temperature on the center / top side of the DRAM. For measurement conditions, please refer to the JEDEC document JESD51-2.

- 2. The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0 85°C under all operating conditions.

- 3. Some applications require operation of the DRAM in the Extended Temperature Range between 85°C and 95°C case temperature. Full specifications are guaranteed in this range, but the following additional conditions apply:

a). Refresh commands must be doubled in frequency, therefore reducing the Refresh interval tREFI to 3.9 µs. It is also possible to specify a component with 1X refresh (tREFI to 7.8µs) in the Extended Temperature Range. Please refer to the DIMM SPD for option availability.

b). If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to either use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 A6 = 0b and MR2 A7 = 1b) or enable the optional Auto Self-Refresh mode (MR2 A6 = 1b and MR2 A7 = 0b).

# AC & DC Operating Conditions

#### **Recommended DC Operating Conditions**

| Symbol | Parameter                          | Rating |      | Unit | NOTE |       |

|--------|------------------------------------|--------|------|------|------|-------|

|        | Farameter                          | Min.   | Тур. | Max. | Unit | NOTE  |

| VDD    | Supply Voltage                     | 1.14   | 1.2  | 1.26 | V    | 1,2,3 |

| VDDQ   | Supply Voltage for Output          | 1.14   | 1.2  | 1.26 | V    | 1,2,3 |

| VPP    | Supply Voltage for DRAM Activating | 2.375  | 2.5  | 2.75 | V    | 3     |

Notes:

- 1. Under all conditions VDDQ must be less than or equal to VDD, this voltage refers to the value of the default frequency.

- 2. VDDQ tracks with VDD. AC parameters are measured with VDD and VDDQ tied together.

- 3. DC bandwidth is limited to 20MHz.

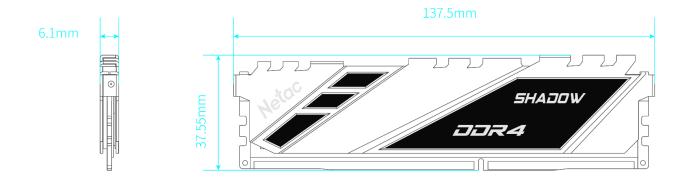

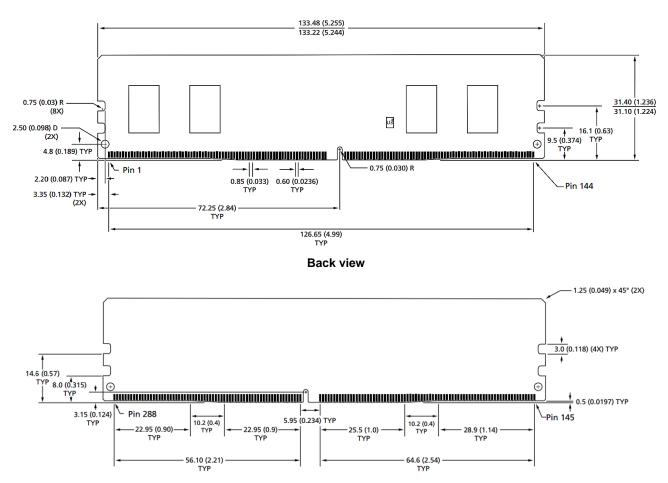

## **Module With Heat Spreader**

## **Module Dimensions**

Netac Technology Co.,Ltd. All rights reserved.

#### Front view

#### Notes:

- 1. All dimensions are in millimeters (inches); MAX/MIN or typical (TYP) where noted.

- 2. Tolerance on all dimensions ±0.15mm unless otherwise specified.

- 3. The dimensional diagram is for reference only.

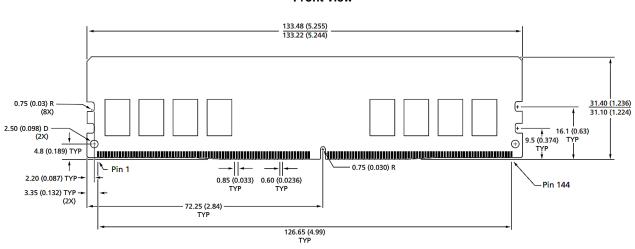

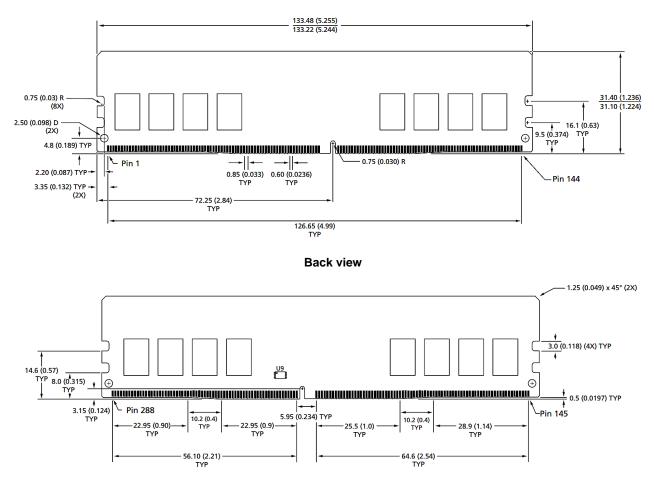

#### Front view

#### Notes:

- 1. All dimensions are in millimeters (inches); MAX/MIN or typical (TYP) where noted.

- 2. Tolerance on all dimensions  $\pm 0.15$ mm unless otherwise specified.

- 3. The dimensional diagram is for reference only.

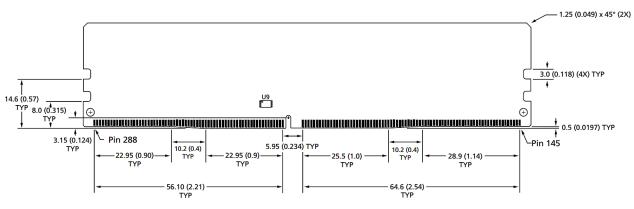

Front view

#### Notes:

- 1. All dimensions are in millimeters (inches); MAX/MIN or typical (TYP) where noted.

- 2. Tolerance on all dimensions ±0.15mm unless otherwise specified.

- 3. The dimensional diagram is for reference only.